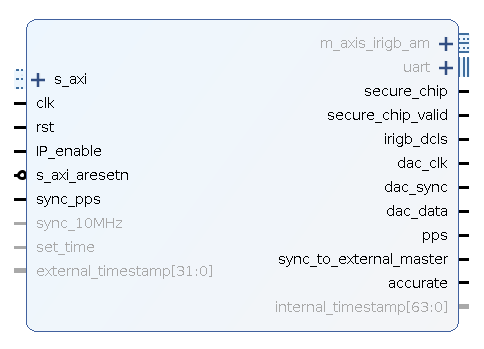

IRIGtimeM implements an IRIG 200-04 compliant time synchronization master on FPGA devices. This IRIG-B master IP has been designed to support all the IRIG-B coded expressions as well as DCLS and AM modulations in order to provide maximum flexibility.

This IRIG-B master IP generates IRIG-B frames each second, including the mandatory and optional time information (seconds, minutes, hours, days, years, control functions and binary straight seconds) depending on the IRIG-B time code selected on the confi

guration. This IP has been designed to provide autonomous operation, requiring as less con

figuration as possible.

IRIGtimeM is supported on the following Xilinx FPGA Families:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

- Managed Ethernet Switch IP Core for Xilinx Vivado Tool -

It is designed to be easily integrated in your FPGA designs by taking advantage of the new Xilinx Vivado Tool, that allows to use the IP Cores in a graphical user interface and configure IP parameters in an easy way.

IRIGtimeM key features:

- IRIG 200-04 compliant time synchronization master

- Support for DCLS and AM modulations

- Support for all IRIG-B coded expressions, including year information, control functions and straight binary seconds

- Output type (IRIG-B timecode) con figurable both before implementation and on the fly

- Precise IRIG-B output in order to provide nanoseconds precision

- 32-bit timestamp input for initial set up of the IP

- Periodic pulse output for testing

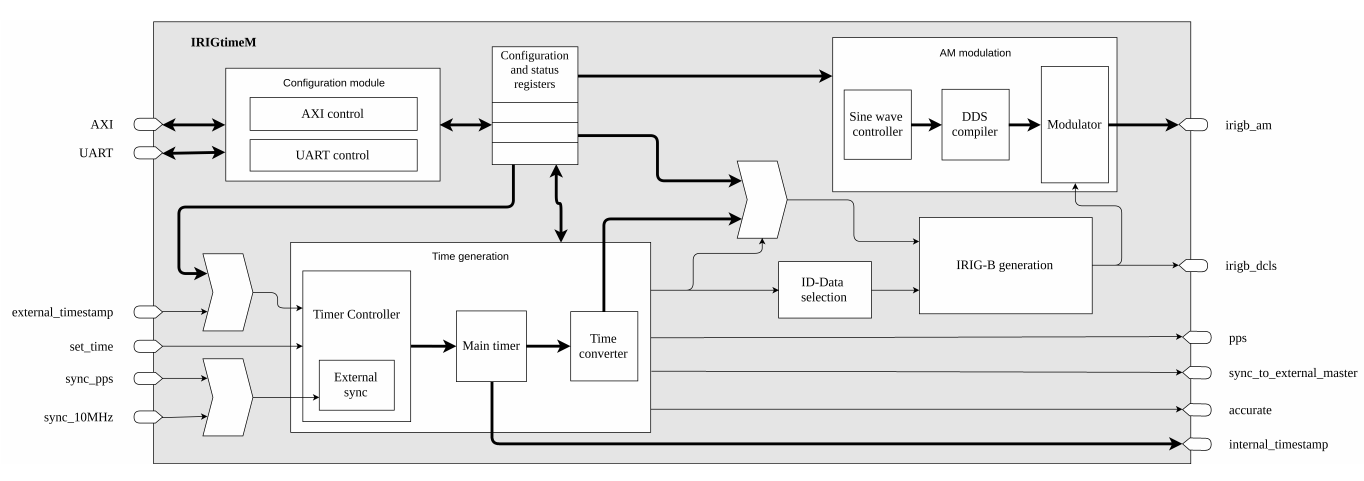

IRIGtimeM IP core block diagram is represented in the following figure:

Supported boards for the Reference Designs:

- SoC-e SMARTzynq brick (Recommended)

- For other Xilinx/Avnet/SoC-e boards, we can provide a time-limited IP Core for evaluation.