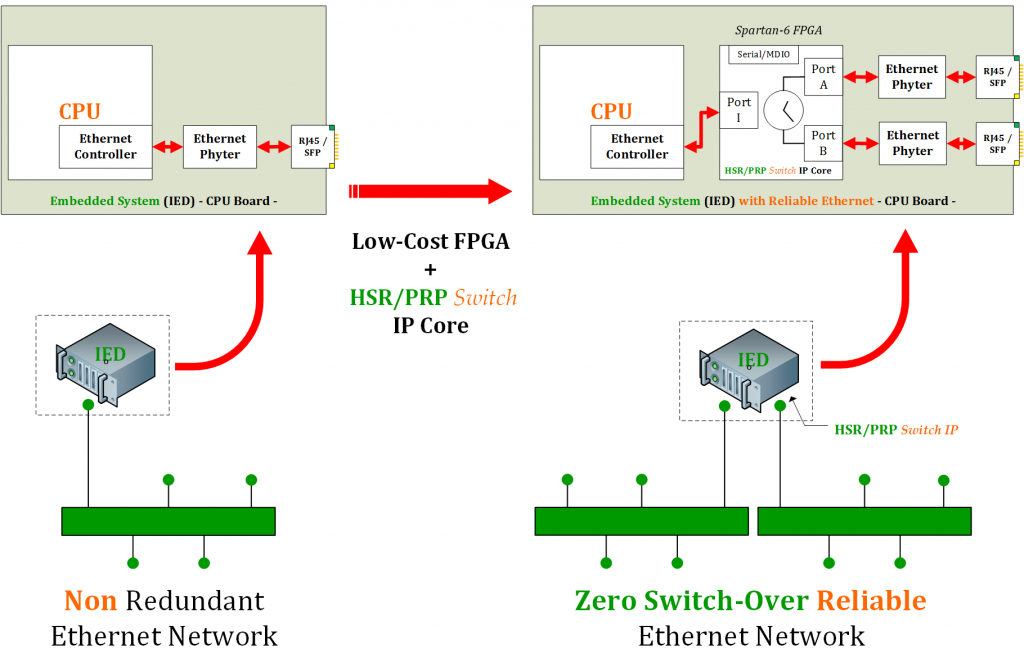

HSR-PRP Switch (HPS) is an IP Core for the implementation of High-availability Seamless Redundancy and Parallel Redundancy Protocol (HSR and PRP version 3, IEC 62439-3-Clause 5 and 4 respectively) standards for Reliable Ethernet communications. HSR-PRP Switch is a full hardware solution that can be implemented on a low-cost FPGA.

It is a flexible solution for the Energy Market Equipment that will be connected to HSR rings, PRP Lans or will work as Network bridges in the context of IEC 61850.

HPS IP Core is supported on the following Xilinx FPGA Families:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

- HSR/PRP Switch IP Core for Xilinx Vivado Tool -

HPS is designed to be easily integrated in your FPGA designs by taking advantage of the new Xilinx Vivado Tool, that allows to use the IP Cores in a graphical user interface and configure IP parameters in an easy way.

HSR-PRP Switch IP core key features:

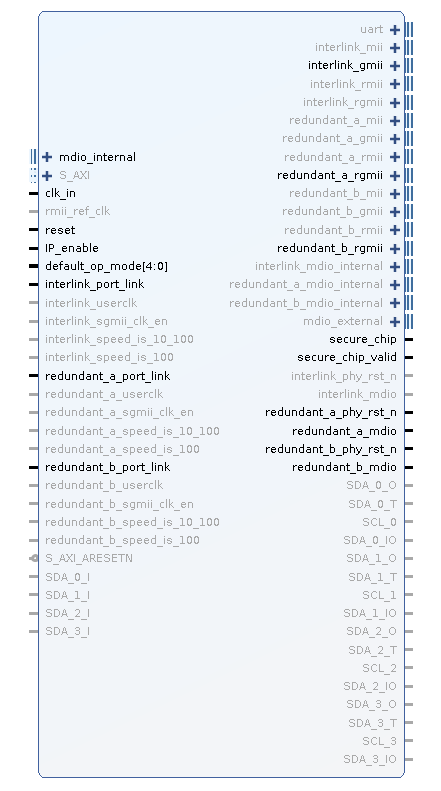

Interfaces

- Full-duplex 10/100/1000 Mbps Ethernet Interfaces

- MII/RMII/GMII/RGMII/SGMII/QSGMII Physical Layer device (PHY) interfaces

- Different data rate supported for each port

- Copper and Fiber optic media interfaces: 10/100/1000Base-T, 100Base-FX, 1000Base-X

Switching

- It switches frames by hardware. This feature offers high switching speeds, needed to fulfill the Maximum Allowed Age and Data Integrity set for Process Bus and Inter-bay Bus in Electric Substation Automation

- The processing architecture has been designed specifically for HSR/PRP. Forwarding latencies in range of 500ns for Gigabit Ethernet

- It is an all-hardware. There is no need for on-chip microprocessor nor software stack

- It has been optimized to require few logic resources in order to allow the implementation on low-cost FPGA devices

- Jumbo Frame Management

Time Synchronization

- It supports IEEE 1588-2008 v2 combined with SoC-e 1588 IP cores

Redundancy

- It can be used to implement End-Node DAN, RedBox or QuadBox functionalities

- It has been provided with a single flag that switches between PRP and HSR modes by software

- It includes complete statistics and error registers for each port integrated (Network Supervision)

- HSR-HSR, HSR-PRP supported modes for seamless PRP-HSR networks merging and Quadbox operation

- VLAN support and HSR Rings ID

- SNMP and MIB Table available

Configuration

- MDIO, UART, AXI4-Lite or CoE (Configuration-over-ethernet) management interfaces

- Configuration-over-Ethernet (COE): Full access to internal registers through the same Ethernet link that connects to the CPU

- Drivers are provided with IP Core purchase

HSR-PRP Switch IP core customizable features for optimum resources/functionalities trade off:

- Node Table size

- Forwarding Queues size independent for each port

- IEEE1588v2 P2P Transparent Clock in Redundant and Interlink Ports

- Scalable duplicate/circulate discard table

- VLAN Priority support

- Access to internal registers via AXI4-Lite, MDIO, UART or CoE (Configuration Over Ethernet)

- RedBox mode with integrated SAN proxy

- IEEE 1588v2 Ordinary Clock, Hybrid Clock and Boundary Clock

- 3 Port Reference for Non Redundant Network VS Zero Switch-Over Reliable Network -

Supported boards for the Reference Designs:

- SoC-e SMARTzynq brick

- Avnet I4EK HSR/PRP Kit

- For other Xilinx/Avnet/SoC-e boards, we can provide a time-limited IP Core for evaluation.