Overview

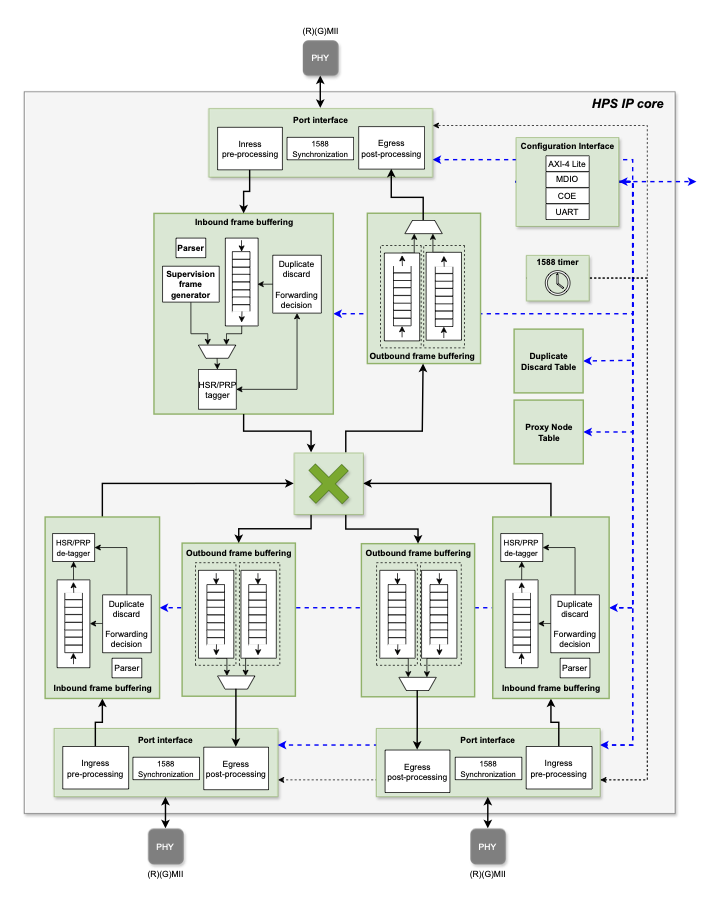

HPS implements the High-availability Seamless Redundancy and Parallel Redundancy Protocol (HSR and PRP, IEC 62439-3 Clause 5 and 4 respectively) Edition 4.0 protocols for Reliable Ethernet communications providing zero recovery time.

It is a full hardware solution that can be implemented in different FPGA families, including low-cost versions. It is a flexible solution for the Electric sector equipment that require to be connected to HSR rings, PRP Lans or to operate as network bridges.

Key Features

- Zero Recovery Time Redundancy Protocol SupportThe IP core implements HSR and PRP redundancy protocols (IEC 62439-3) providing seamless Ethernet redundancy.

- Lowest Latency in HSRThanks to the implementation of cut-through between ring ports.

- High-performanceUp-to 1G interfaces.

- Fast & Smooth IntegrationFast & smooth Integration: GUI available for some FPGA vendor tools (i.e., AMD Vivado™ Design Suite) included as part of the product deliverable.

- Evaluation Version AvailableEncrypted, time-limited version available.

Technical Specifications

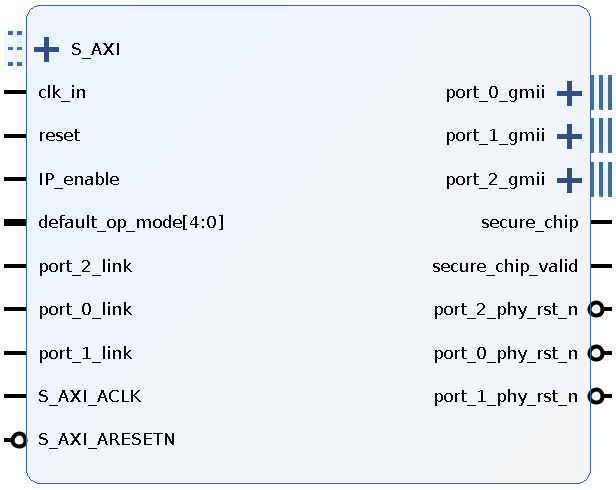

- Communication Interfaces

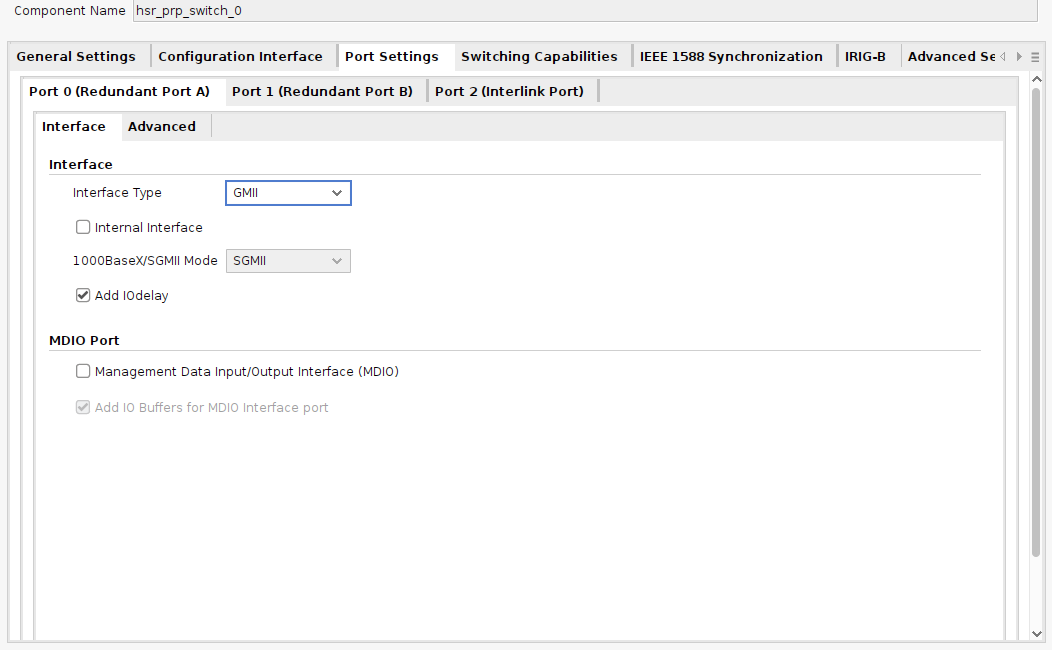

- Integrated 10M/100M/1000M MACs for 10/100 Mbps and 1 Gbps PHY interface rates to use with any PHY interface type (e.g. MII, RMII, GMII, RGMII) depending on application

- Compatible with SGMII (Serial Gigabit Media Independent Interface) or QSGMII (Quad Serial Gigabit Media Independent Interface) PHY interfaces throughout an internal GMII based connection to AMD LogiCORE™ SGMII IP core and LogiCORE™ QSGMII IP core respectively

- 10/100/1000 Mbps AXI-Stream interface with a data width of 8 bits @ 125 MHz

- Redundancy

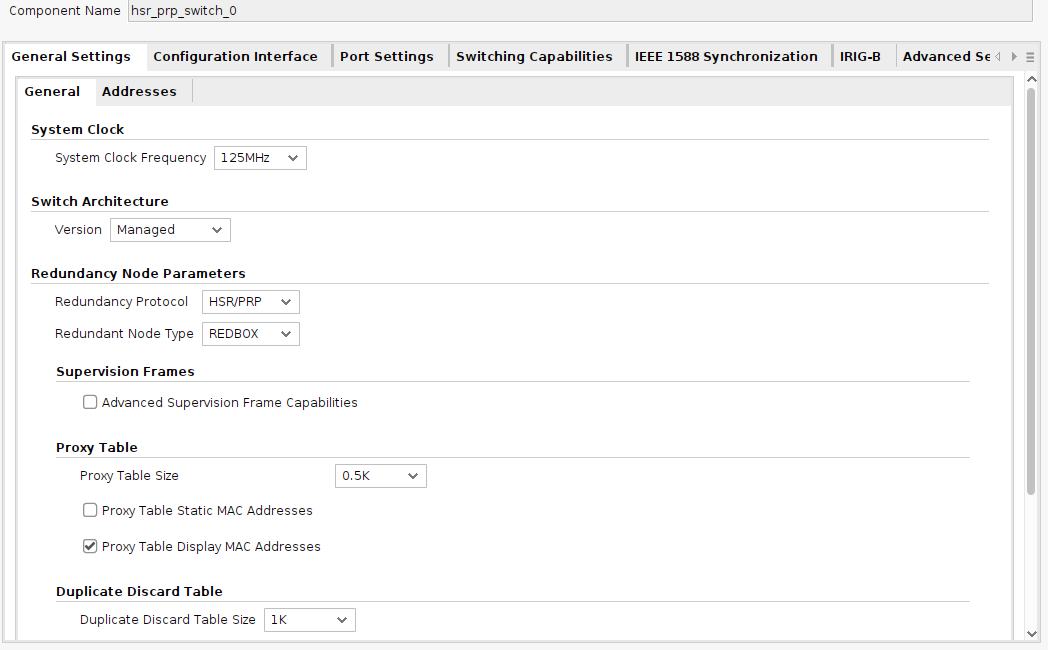

- High-availability Seamless Redundancy (HSR). It can operate in any of the following modes, which are changeable at runtime:

- Mode H (mandatory, default mode): HSR-tagged forwarding

- Mode M (optional): Mixed forwarding HSR-tagged and non HSR-tagged

- Mode N (optional): No forwarding

- Mode T (optional): Transparent forwarding

- Mode U (optional): Unicast forwarding

- Mode R (optional): For RedBoxes to be connected to an RSTP bridge

- Parallel Redundancy Protocol (PRP). It can operate in any of the following modes, which are changeable at runtime:

- Duplicate Discard (default mode)

- Duplicate Accept (testing only)

- In HSR mode, the RedBox can work on one of the following three modes:

- HSR-SAN: the traffic on the interlink is not HSR, not PRP

- HSR-PRP: the traffic on the interlink is PRP-tagged

- HSR-HSR: the traffic on the interlink is HSR-tagged

- Configurable size Redundancy Proxy Node Table to keep information about all nodes that are attached to the interlink port

- Configurable size Redundancy Duplicate Discard Table used to discard duplicate frames received from redundant ports

- Traffic Management

- Cut-through forwarding between redundant ring ports for a very low forwarding latency independent from frame size

- MAC Level Ingress Frame Filtering based of Destination MAC address and/or Ethertype on per port basis

- Custom Destination MAC filtering and forwarding (up to 16 MAC addresses can be filtered)

- Custom Source MAC filtering and forwarding (up to 10 MAC addresses can be filtered)

- Standard Frame size support (1518) or Jumbo frames up to 9 kByte (depends on memory availability)

- Time Synchronization

- IEEE1588 (PTPv2): IEEE1588 Stateless Transparent Clock (SLTC) functionality at layer-2 and peer-to-peer (P2P)

- IEEE1588 Hybrid Clock (HC) slave-only support

- IEEE 1588-2008 (PTPv2) slave-only compliant clock synchronization

- One Pulse-Per-Second (PPS) output available

- Event timestamping supported (up-to 4 different events simultaneously)

- Alarm detection supported (up-to 4 different alarms simultaneously)

- IRIG-B Master support

- IRIG 200-04 compliant time synchronization master

- Support for DCLS modulation

- Support for all IRIG-B coded expressions, including year information, control functions and straight binary seconds

- IEEE1344 extension support

- Output type (IRIG-B time code) configurable both before implementation and on the fly

- Implements a generic DAC controller compatible with SPI, QSPI and MICROWIRE protocols

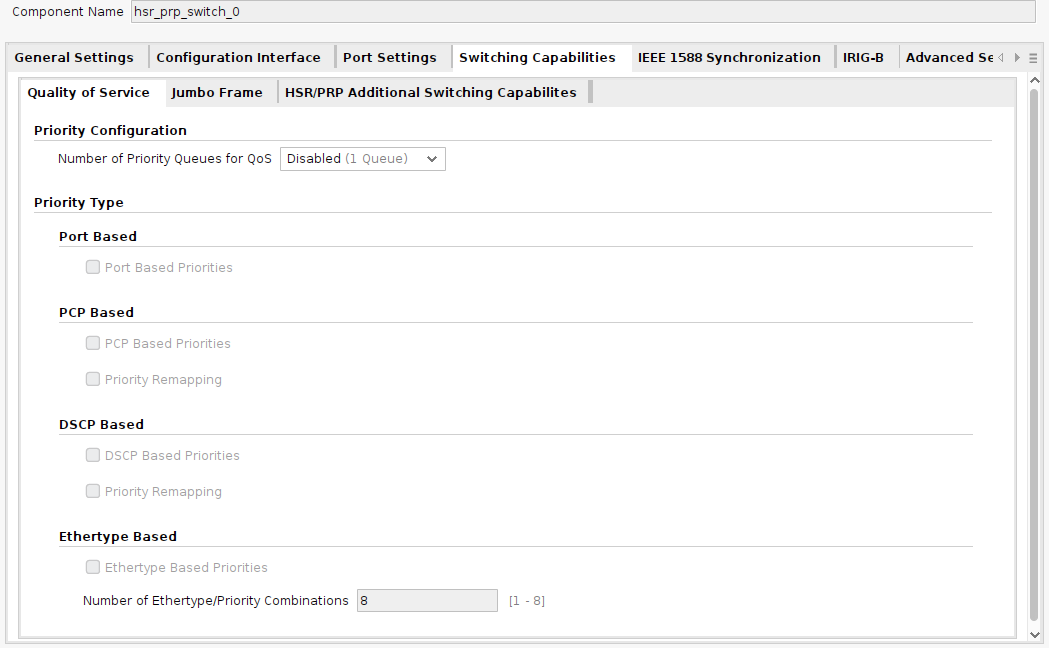

- Quality of Service

- QoS support with up to 8 priority queues per port (synthesis option)

- Priority classification based on Ingress Port, PCP bits (802.1p), DSCP TOS bits of the IP packets (IPv4 TOS/IPv6 COS) and Ethertype

- Programmable remapping from PCP or DSCP fields to internal priority queues on a per-port basis

- Traffic prioritization based on Strict priority scheduling algorithm

- MAC Level Ingress Frame Rate Limiting on per port basis

- Network Management & Monitoring

- Per port MAC and switch statistics for managing and debugging purposes

- Wide range of management interfaces to access control and statistics registers (selectable at synthesis time)

- I2C master interface for external device configuration (i.e. an EEPROM memory with non-volatile configuration)

Technical Support, Verification & Deliverables

Technical Support

IP Licenses are provided along with a Technical Support package that ensures a direct communication channel with our highly experienced support engineers. This is vastly valued during customer product development & integration phases.

Verification

All our IP Cores are rigorously tested, hardware-validated and verified in real-life environments. A 3-phase based IP product verification is applied:

- Entity/Block-oriented simulation

- Global-oriented simulation

- In-hardware validation

Deliverables

- Encrypted/Source RTL code

- Software components: Drivers, configuration API & SW stacks

- Documentation (IP Core and Software components)

- (Optional) Networking Testbench Suite (NTS)

- (Optional) AMD Vivado™ design suite example design

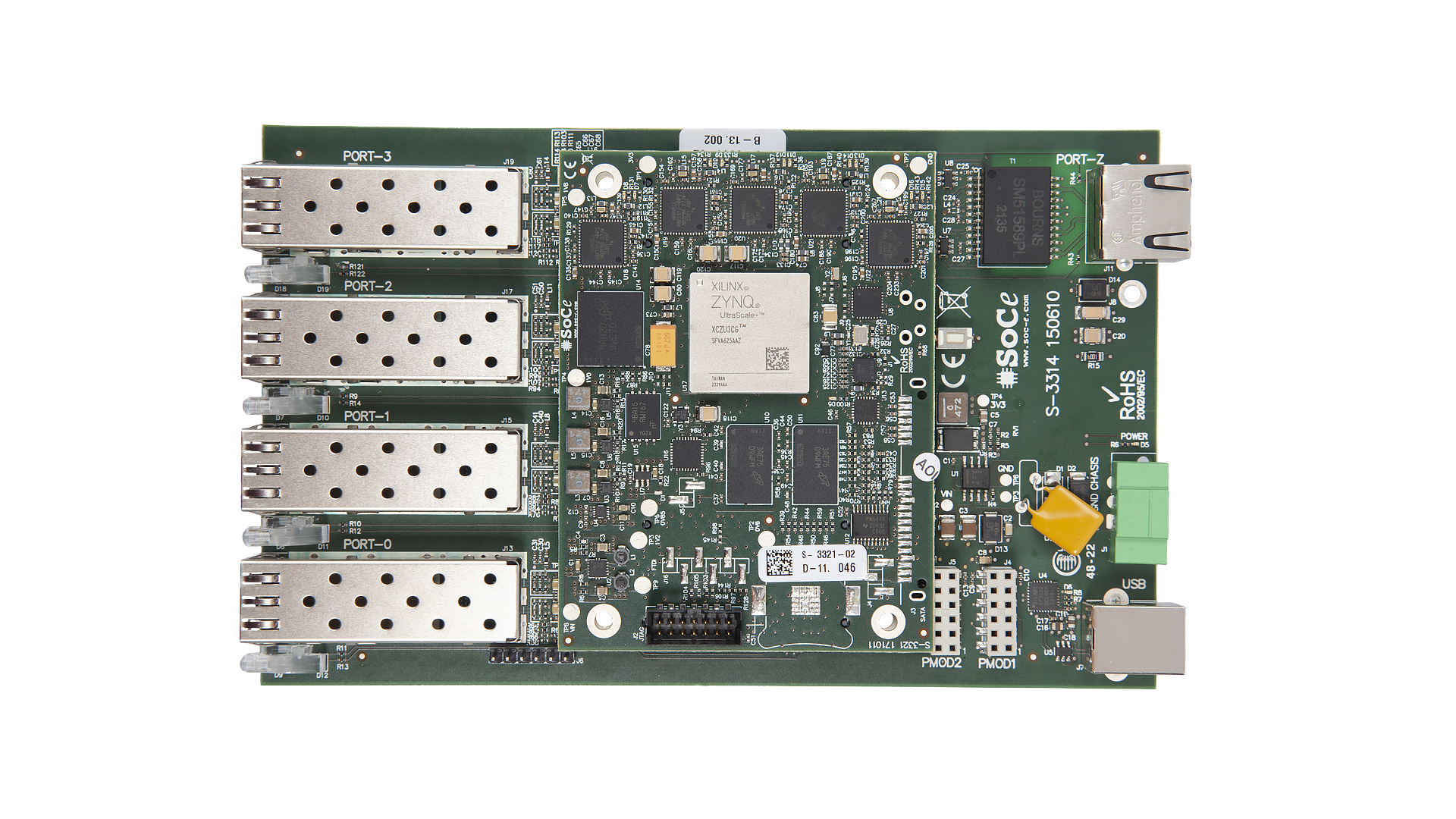

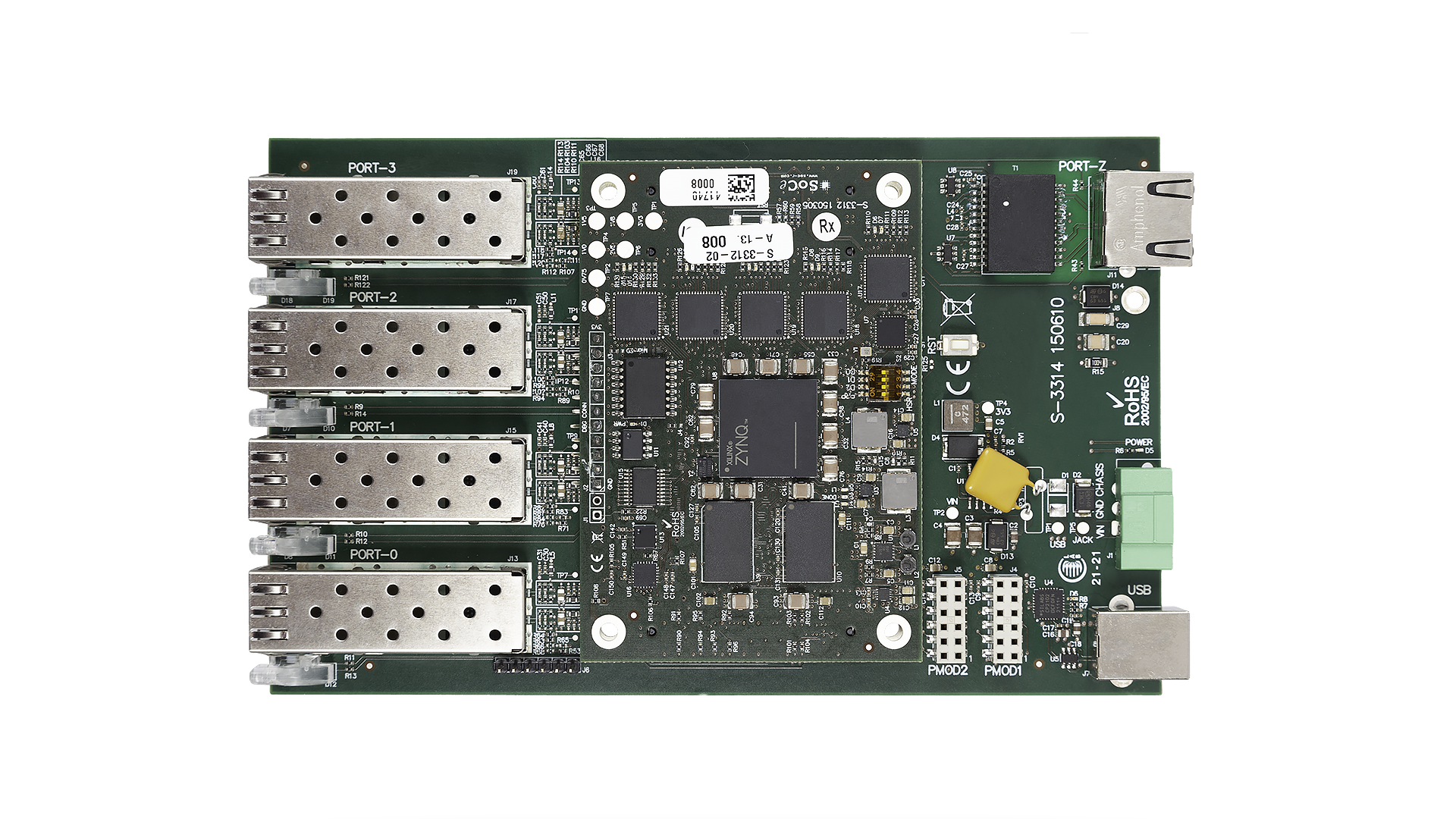

Evaluation & Design-in Kit

This hardware can also be used later as a development platform, what allows to shorten the development phase.