Overview

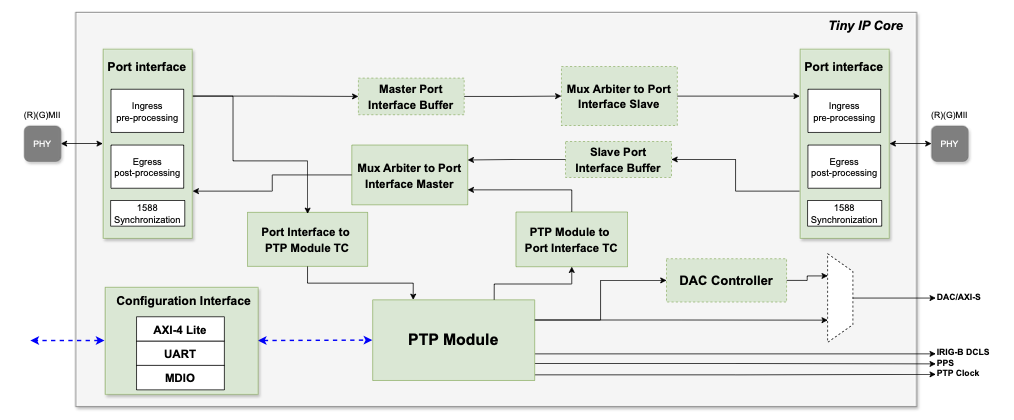

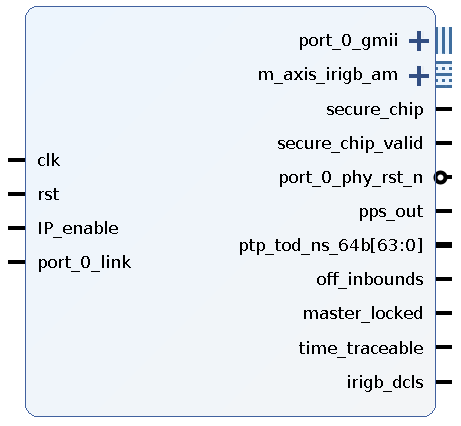

1588Tiny is a hardware-only (VHDL) IP Core that implements an IEEE1588-2008 (Version 2) PTP slave / time receiver clock for FPGA. It provides submicrosecond clock synchronized to the network PTP Master.

This solution does not require the use of an external PTP software stack running on an embedded CPU. It’s an all-in-one PTP slave implementation.

It provides an excellent trade-off between a good enough clock accuracy and limited hardware resources (gates, memory, etc…) in a standalone product.

Key Features

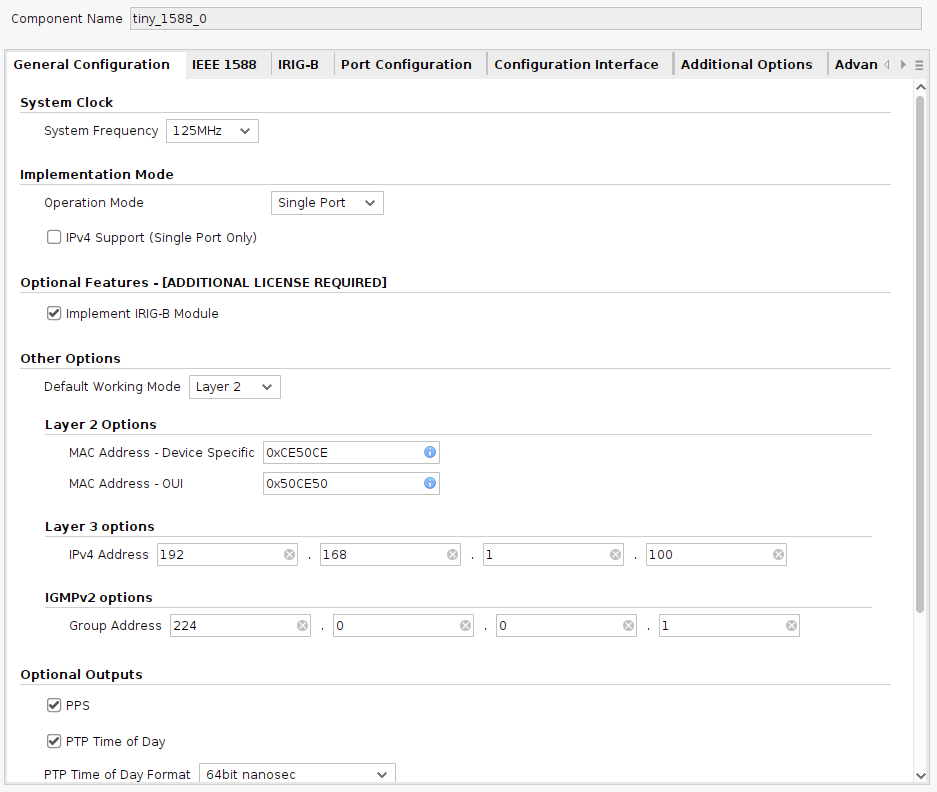

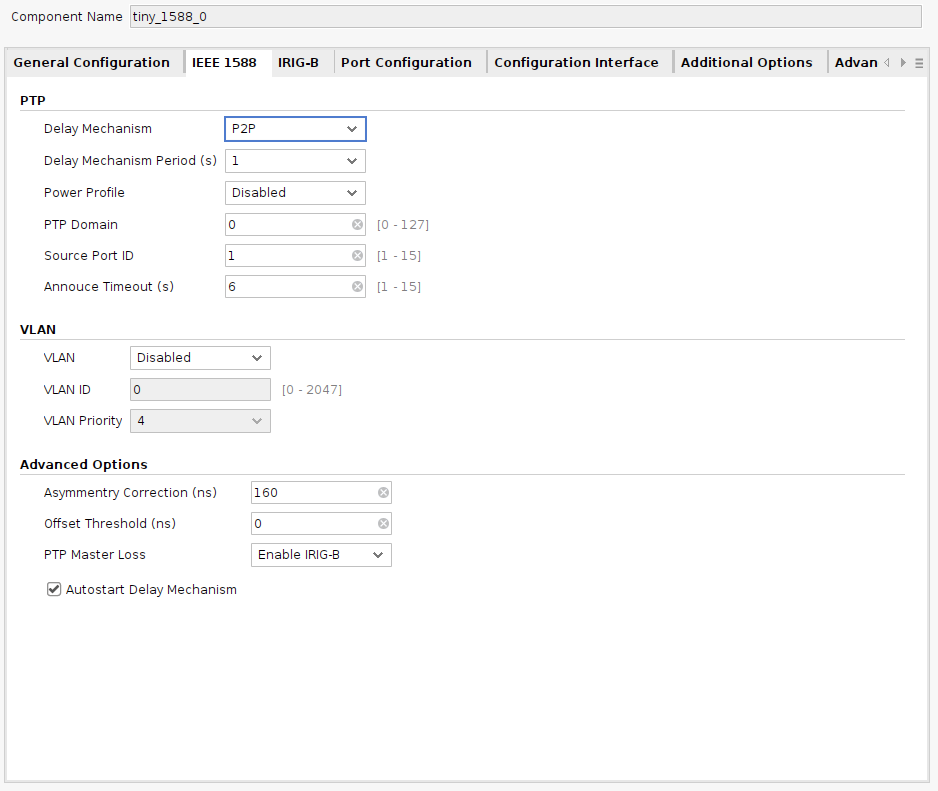

- Multi-PTP Profile CapableDesigned to support Default and Power Utility Profile (IEC/IEEE 61850-9-3) with multiple configurations (Layer-2/Layer-3, E2E/P2P, etc…).

- PTP Slave / Time Receiver to IRIG-B Master / Time Transmitter Bridge FunctionalityProvides an IRIG-B (DCLS modulation) master reference using the internal PTP Timer as its time source.

- Dual Port (passthrough) ModeAvoids consuming the ethernet port strictly for PTP communication by enabling a second ethernet port.

- Event Timestamping and Alarm Detection SupportedBased on the PTP timer clock, allowing the user to retrieve timestamps directly from a register.

- Fast & Smooth IntegrationGUI available for some FPGA vendor tools (i.e., AMD Vivado™ Design Suite).

- Evaluation Version AvailableEncrypted, time-limited version available.

Technical Specifications

- Time Synchronization

- 64bit nanoseconds and 48bit seconds / 32bit nanoseconds selectable ToD PTP Clock output

- One pulse per second (PPS) output available

- Layer-2 (PTP over ethernet) and Layer-3 (PTP over UDP) supported

- Event timestamping supported (up to 4 different events simultaneously)

- Alarm detection supported (up to 4 different alarms simultaneously)

- Optional IRIG-B master output synchronized with the PTP internal timer

- IRIG 200-04 compliant time synchronization master

- Support for DCLS modulation

- Support for all IRIG-B coded expressions, including year information, control functions and straight binary seconds.

- IEEE1344 extension support.

- Output type (IRIG-B time code) configurable both before implementation and on the fly.

- Generic DAC controller implementable compatible with SPI, QSPI and MICROWIRE protocols.

- Communication Interfaces

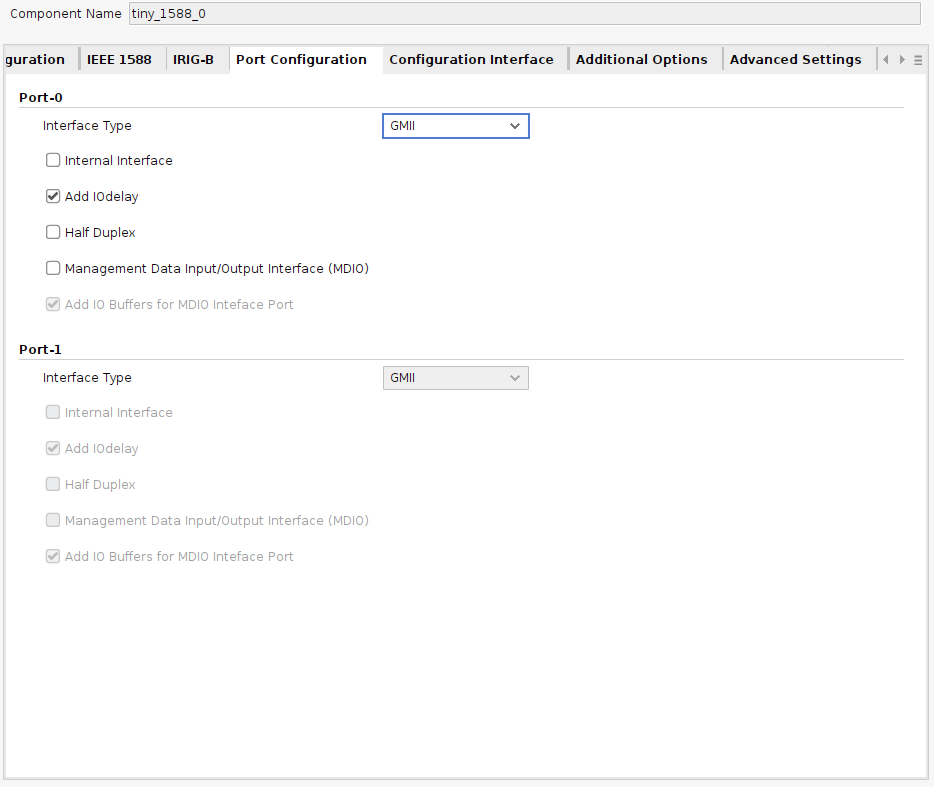

- Integrated 10M/100M/1000M MACs for 10/100 Mbps and 1 Gbps PHY interface rates to use with any PHY interface type (e.g. MII, GMII, RGMII) depending on application

- Compatible with SGMII (Serial Gigabit Media Independent Interface) or QSGMII (Quad Serial Gigabit Media Independent Interface) PHY interfaces throughout an internal GMII based connection to AMD LogiCORE™ SGMII IP core and LogiCORE™QSGMII IP core respectively

- 10/100/1000 Mbps AXI-S interface with a data width of 8 bits @ 125 MHz

- Network Management & Monitoring

- IGMP version 2 protocol supported for Layer-3 (PTP over UDP) operation, allowing 1588Tiny to join multicast IPv4 networks

- Per port MAC statistics for managing and debugging purposes

- Wide range of management interfaces to access control and statistics registers (selectable at synthesis time)

Technical Support, Verification & Deliverables

Technical Support

IP Licenses are provided along with a Technical Support package that ensures a direct communication channel with our highly experienced support engineers. This is vastly valued during customer product development & integration phases.

Verification

All our IP Cores are rigorously tested, hardware-validated and verified in real-life environments. A 3-phase based IP product verification is applied:

- Entity/Block-oriented simulation

- Global-oriented simulation

- In-hardware validation

Deliverables

- Encrypted/Source RTL code

- Documentation (IP Core datasheet)

- (Optional) AMD Vivado™ design suite example design