Overview

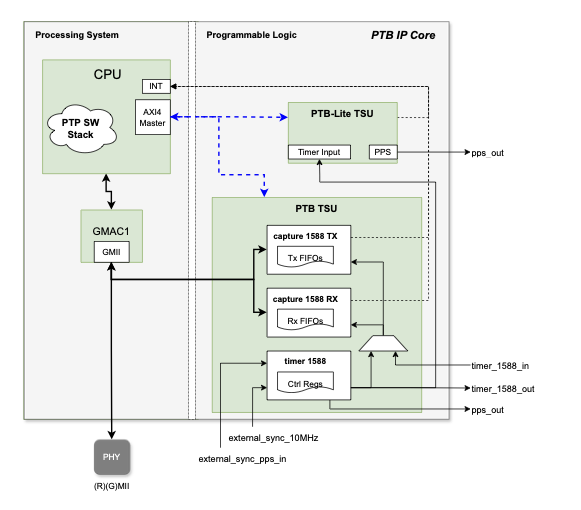

PreciseTimeBasic is a PTP Ordinary (master / time transmitter & slave / time receiver) capable clock for System-on-Programable Chip (SoPC). As a time receiver it provides nanosecond level clock synchronized to network PTP time transmitter. As a time transmitter it generates all the required PTP frames.

This solution is composed by three main components: An IP Core for FPGA that implements the timestamping unit (TSU); a PTP stack for Linux operating system (running on the in-built SoPC processor) and a driver (provided as a patch for Linux kernel).

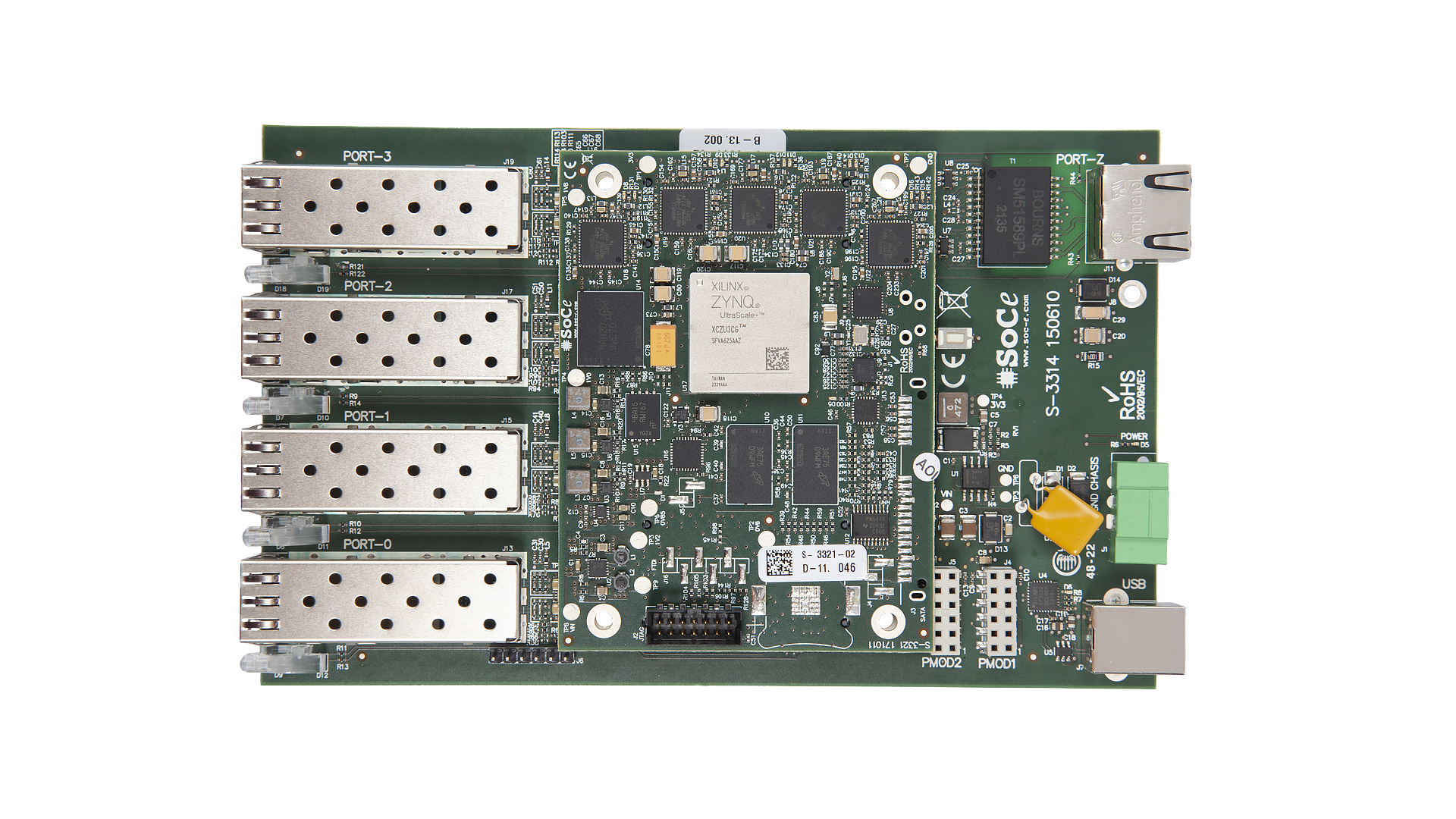

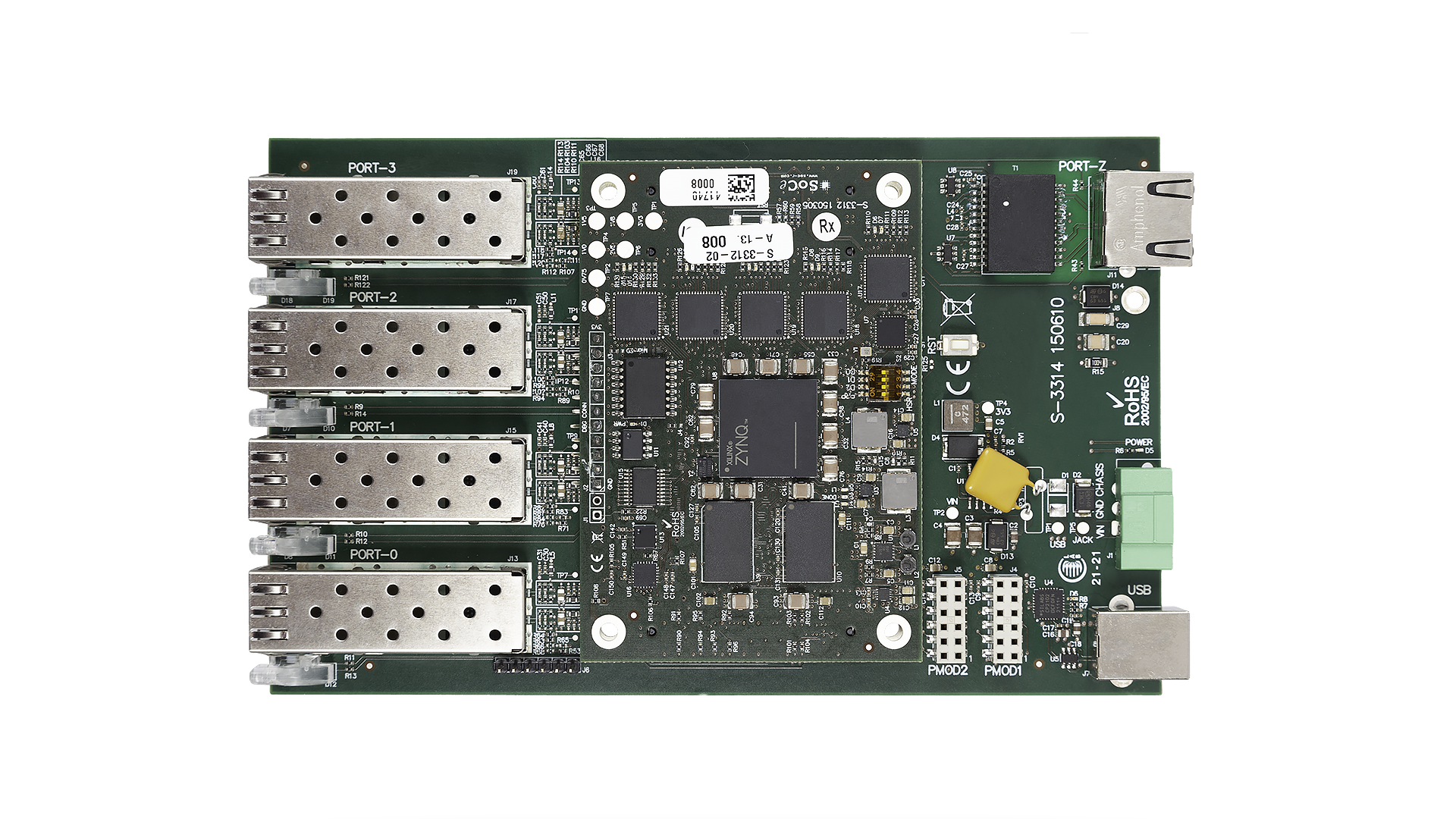

PreciseTimeBasic IP Core is specifically designed for AMD/Xilinx SoPC platforms, specifically Zynq®-7000 & Zynq®UltraScale+ MPSoC families.

This product provides higher accuracy and flexibility compared to SOC-E 1588Tiny IP Core by making use of a software PTP stack.

Key Features

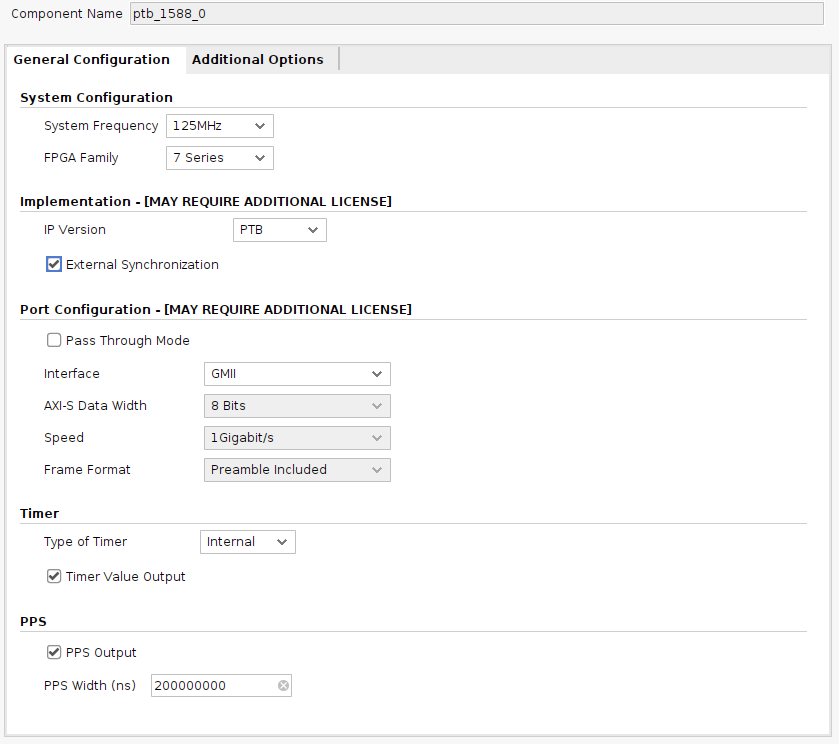

- Multi-PTP Profile CapableDesigned to support Default and Power Utility Profile (IEC/IEEE 61850-9-3) with multiple configurations (Layer-2/Layer-3, E2E/P2P, etc…).

- PTP Time Transmitter (master) and Time Receiver (slave) CapableBoth operation modes supported in the same implementation.

- Event Timestamping and Alarm Detection SupportedBased on the PTP timer clock, allowing the user to retrieve timestamps directly from a register.

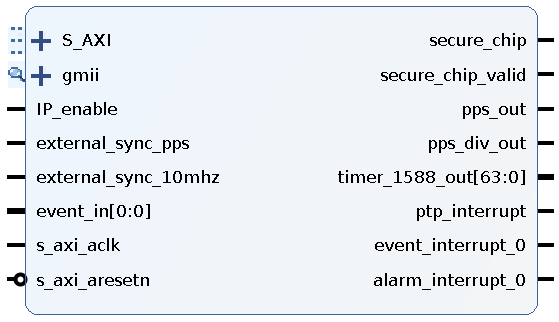

- Fast & Smooth IntegrationGUI available for some FPGA vendor tools (i.e., AMD Vivado™ Design Suite). Drivers & software components included as part of the product deliverable.

- Evaluation Version AvailableEncrypted, time-limited version available.

Technical Specifications

- Communication Interfaces

- Integrated 10M/100M/1000M MACs for 10/100 Mbps and 1 Gbps PHY interface rates to use with any PHY interface type (e.g. MII, GMII, RGMII) depending on application

- Compatible with SGMII (Serial Gigabit Media Independent Interface) or QSGMII (Quad Serial Gigabit Media Independent Interface) PHY interfaces throughout an internal GMII based connection to AMD LogiCORE™ SGMII IP core and LogiCORE™QSGMII IP core respectively

- Configurable AXI-Stream interfaces to support several data rates.

- 1000/10000/25000 Mbps AXI-S interface with a data width of 64 bits @ 156.25 MHz.

- Time Synchronization

- 32bit nanoseconds and 32bit seconds ToD PTP Clock output

- One pulse per second (PPS) output available

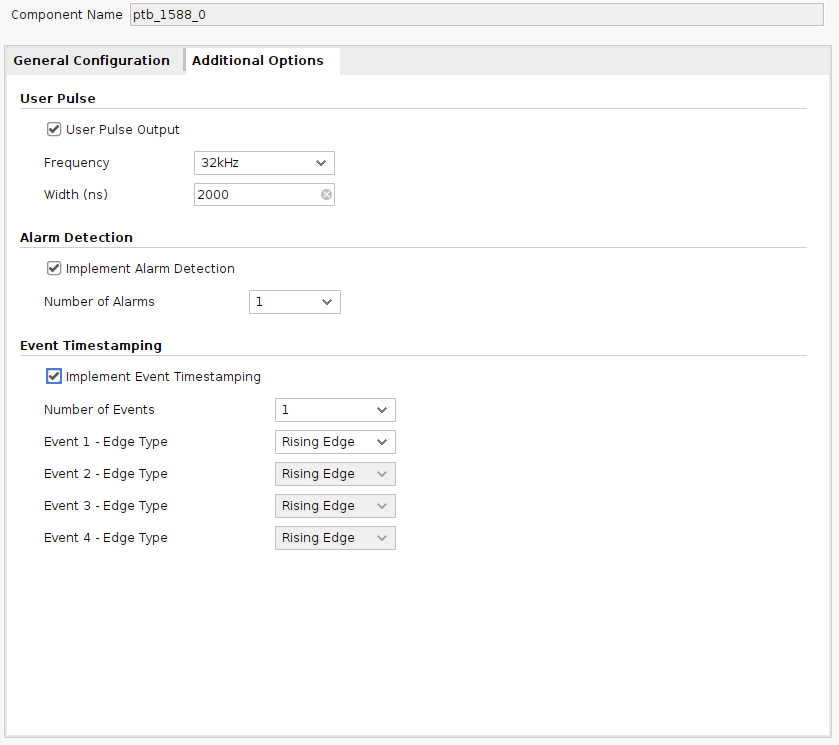

- One Frequency Selectable pulse output available (1kHz/ 2kHz/ 4kHz/ 8kHz/ 16kHz/32kHz).

- Layer-2 (PTP over ethernet) and Layer-3 (PTP over UDP) supported

- Event timestamping supported (up to 4 different events simultaneously).

- Alarm detection supported (up to 4 different alarms simultaneously).

- Network Management & Monitoring

- Per port MAC statistics for managing and debugging purposes.

- AXI4-Lite management interfaces to access control and statistics registers.

Technical Support, Verification & Deliverables

Technical Support

IP Licenses are provided along with a Technical Support package that ensures a direct communication channel with our highly experienced support engineers. This is vastly valued during customer product development & integration phases.

Verification

All our IP Cores are rigorously tested, hardware-validated and verified in real-life environments. A 3-phase based IP product verification is applied:

- Entity/Block-oriented simulation

- Global-oriented simulation

- In-hardware validation

Deliverables

- Encrypted/Source RTL code

- Software components: Drivers, configuration API & SW stacks

- Documentation (IP Core datasheet)

- (Optional) AMD Vivado™ design suite example design

Evaluation & Design-in Kit

This hardware can also be used later as a development platform, what allows to shorten the development phase.