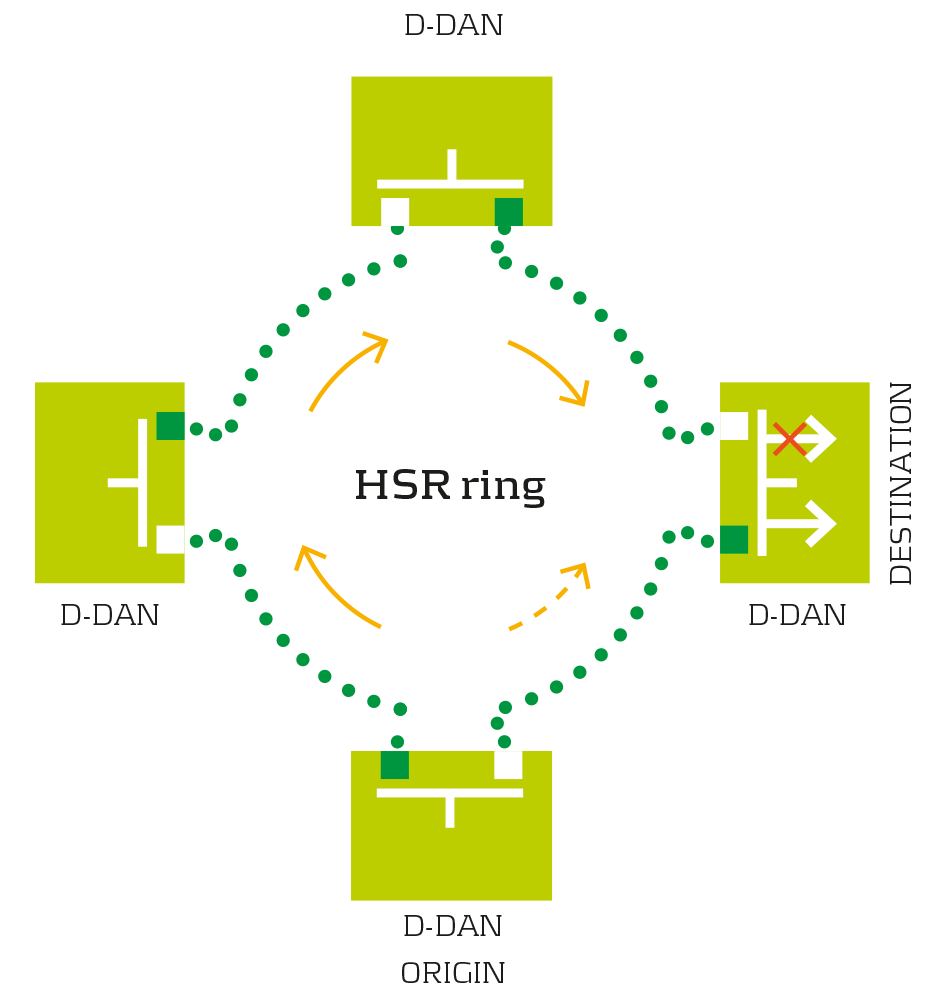

High-availability Seamless Redundancy (HSR, IEC 62439-3-Clause 5) provides redundancy by sending packets in both directions through a ring network. In case of an interruption in the ring, a HSR capable destination node always receives the frames through one other port.

The IEC 62439-3-Clause 5 standard defines priority for the traffic received from the ring. Therefore, it is feasible calculating the worst case scenario for the delivery of a message within a HSR ring. This behavioral allows using standard HSR in some real-time environments.

However, if the timing and bandwidth use restrictions are severe, it is necessary adding a timing plane to the HSR nodes in order to deliver the data traffic in an scheduled way. IEEE 1588 protocol is the driver to build a deterministic HSR solution focused on rugged sectors like Electric or Defense that prefers a robust hardware based solution simpler than the general purpose TSN one.

Deterministic HSR (DHSR) IP core is a proprietary hardware based solution optimized for reconfigurable devices ready for being upgrade if IEC releases a final inter-operable standard for Deterministic High-availability Seamless Redundancy.

Deterministic HSR (DHSR) IP Core Key Features:

- Deterministic precise frame sending in HSR

- Cyclic time-division multiplexing based on precise clock synchronization

- General features listed for HSR/PRP Switch IP product