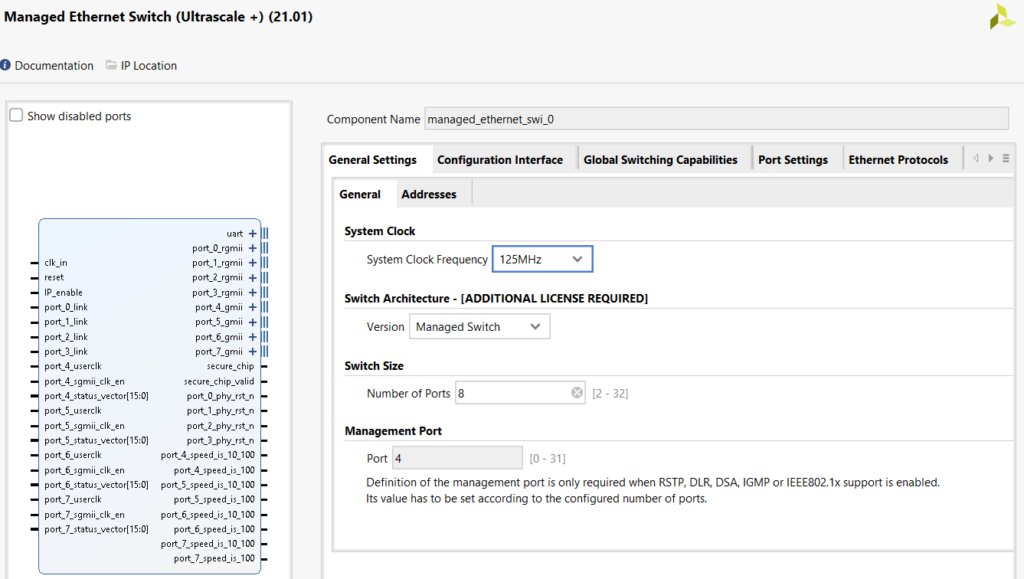

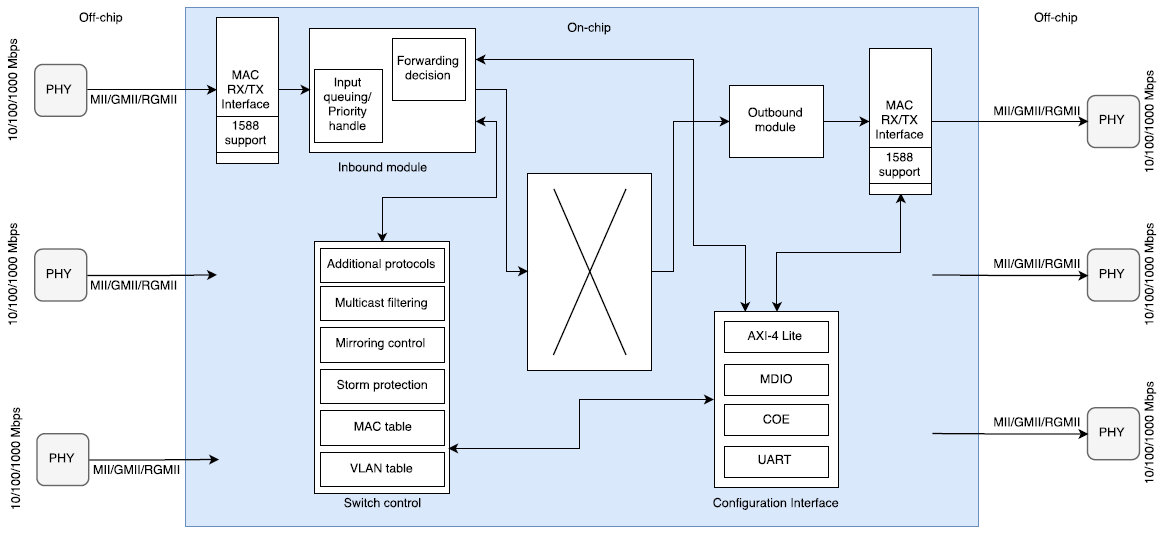

Managed Ethernet Switch (MES) is an Ethernet switch IP Core targeted at programmable hardware platforms like FPGAs and reconfigurable SoCs. Our Managed Ethernet Switch is a Networking IP Core that features a non-blocking crossbar matrix that allows continuous transfers between all the ports. Implementing a Store & Forward switching approach, the switch buffers and verifies each frame before forwarding it. Besides, the latency time is in the order of nanoseconds. So, MES is the perfect switch to implement Ethernet based Industrial Networks. Moreover, It can also be used in other applications. Thanks to the FPGA technology, our IP Cores are highly configurable, offering a wide range of options. In this case, our MES IP Core can go from a simple 3 port Ethernet Switch to a 32 port Ethernet Switch with QoS and RSTP for example. MES can be combined with SoC-e’s IP Cores like the HSR-PRP Switch IP Core, introducing HSR and PRP capabilities in the ports in which it is required. HSR switching approach is Cut Through. Thus, the combination offers the greatest performance and compatibility with the standards. Highly configurable Ethernet Switch Managed Ethernet Switch IP Core block diagram Our MES IP Core can be deployed in the following Xilinx families. You can find the different Xilinx product tables and selection guides at the following links: When it comes to Evaluation boards, at SoC-e we also develop System-on-Modules (SoMs) that we can provide with a preloaded design of our IP Cores. In this case, our recommendation would be the SMARTzynq brick solution, which has a 7-Series Zynq Xilinx FPGA. If the 7-Series Zynq device is not what you are looking for, we have other SoMs based on Ultrascale or Ultrascale+ Xilinx FPGA Families. For other Xilinx/Avnet/SoC-e/ boards, we can provide a time-limited IP Core for evaluation.

Managed Ethernet Switch IP Core key features

Interfaces

Switching

Time Synchronization

Redundancy Protocols

Supported Xilinx FPGA Families and Evaluation boards