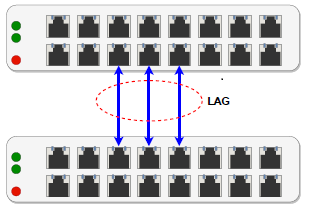

Link Aggregation according to IEEE 802.1AX-2008 (formerly IEE 802.3ad) is a standard for bundling multiple network connections in parallel (Link Aggregation Groups – LAGs) as it is shown in the next figure:

Link Aggregation has the following properties:

- LAG provides link redundancy (fault tolerance) and automatic recovery when individual physical links fail. If one of the ports of the LAG fails, the other ports will automatically provide backup and share the traffic.

- Data transmission will be distributed over the physical links.

- All the frames belonging to any individual session (the same data flow) always take the same link inside the LAG and, thus, ensures the correct sequence of data transmission and prevents misordering.

Link aggregation distributes Ethernet frames among all physical links available in a LAG connection. Thereby, the potential data throughput can exceed the data rate of a single physical link. Although the IEEE standard does not de fine a speci fic algorithm for frame distribution, there are some individual guidelines:

- The order of frames for a speci fic data communication packet should be maintained (prevent packet misordering).

- Frames may not be duplicated.

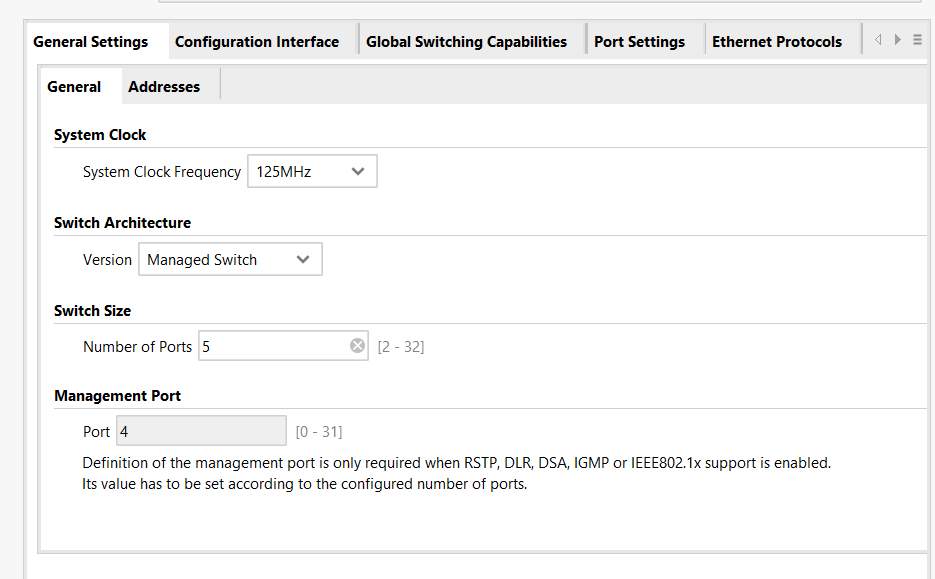

Managed Ethernet Switch (MES) IP core now supports Static Link Aggregation which enables a number of ports to be configured to form a single logical connection of higher bandwidth.

MES is a tri-speed (10/100/1000 Mpbs) switch IP and supports IEEE 1588 V2 Transparent Clock functionalities. It has been designed to be easily integrated in your FPGA designs by taking advantage of Xilinx Vivado Tool, that allows using the IP Cores in a graphical user interface and configuring IP parameters in an easy way.

We also have the 10G MES, for higher speeds: 100M/1G/2.5G/5G/10G.

System-on-Chip engineering S.L. (SoC-e) is a worldwide leading supplier of time-aware Ethernet networking solutions. SoC-e is pioneer in developing a portfolio of IP cores and rugged platforms that implement these technologies for critical systems.