Nowadays, sectors like Industry, Medical and A&D demand 10G Ethernet capable equipment. In addition to these high-speed ports, it is usual requiring large number of ports and media-speed combination in the Ethernet switch fabric.

FPGA and Reconfigurable SoCs are popular in the added-value equipment for these sectors. They are used to integrate the Ethernet switch fabric in combination with other application dependent IPs. The implementation of big number and high-throughput capable Ethernet ports increments drastically the FPGA internal resources needed for the implementation. These resources are cost-sensitive. Thus, the selection of an Ethernet Switch IP not optimized with the best internal architecture could impact on the competitiveness of the final product.

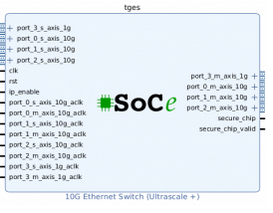

SoC-e‘s 10G Managed Ethernet Switch (TGES) includes Port Grouping feature. TGES makes use of internal high-speed data-paths for the connection of the different ports towards the switch matrix. The use of the Port Grouping feature allows combining sub-10Gbps ports (100M/1G/2.5G/5G ports) into “clusters”. As an example, 5x1G ports and 2×2.5G ports can be combined into a single cluster, allowing to downscale the FPGA resource usage.

Moreover, the calculation of the optimal port distribution within the cluster(s) is automatically performed by the IP Core in synthesis time, so the user does not even have to manually perform the distribution. Easy, and time-effective!

The TGES IP Core offers a FPGA resources saving up to 40%-off compared to a Ethernet Switching solution without this improvement.

10G Managed Ethernet Switch (TGES) is a multi-speed (100M/1G/2.5G/5G/10G) switch IP and supports IEEE 1588 V2 Transparent Clock functionalities. This feature modifies PTP event messages taking into account the time spent crossing the switch. This scheme improves distribution accuracy by compensating delivery variability across the network. Specifically, TGES supports IEEE 1588 V2 One Step Transparent Clock Peer-to-Peer (P2P) functionality by using independent hardware for each port. This feature allows compensating the residence time but also the delay of each link.

SoC-e is a worldwide leading supplier of Ethernet communication solutions based on FPGA technology. SoC-e is pioneer in developing a portfolio of IP cores that implement the leading-edge networking, synchronization and security technologies for critical systems.

For more information, please contact us at: info@soc-e.com