Latest News

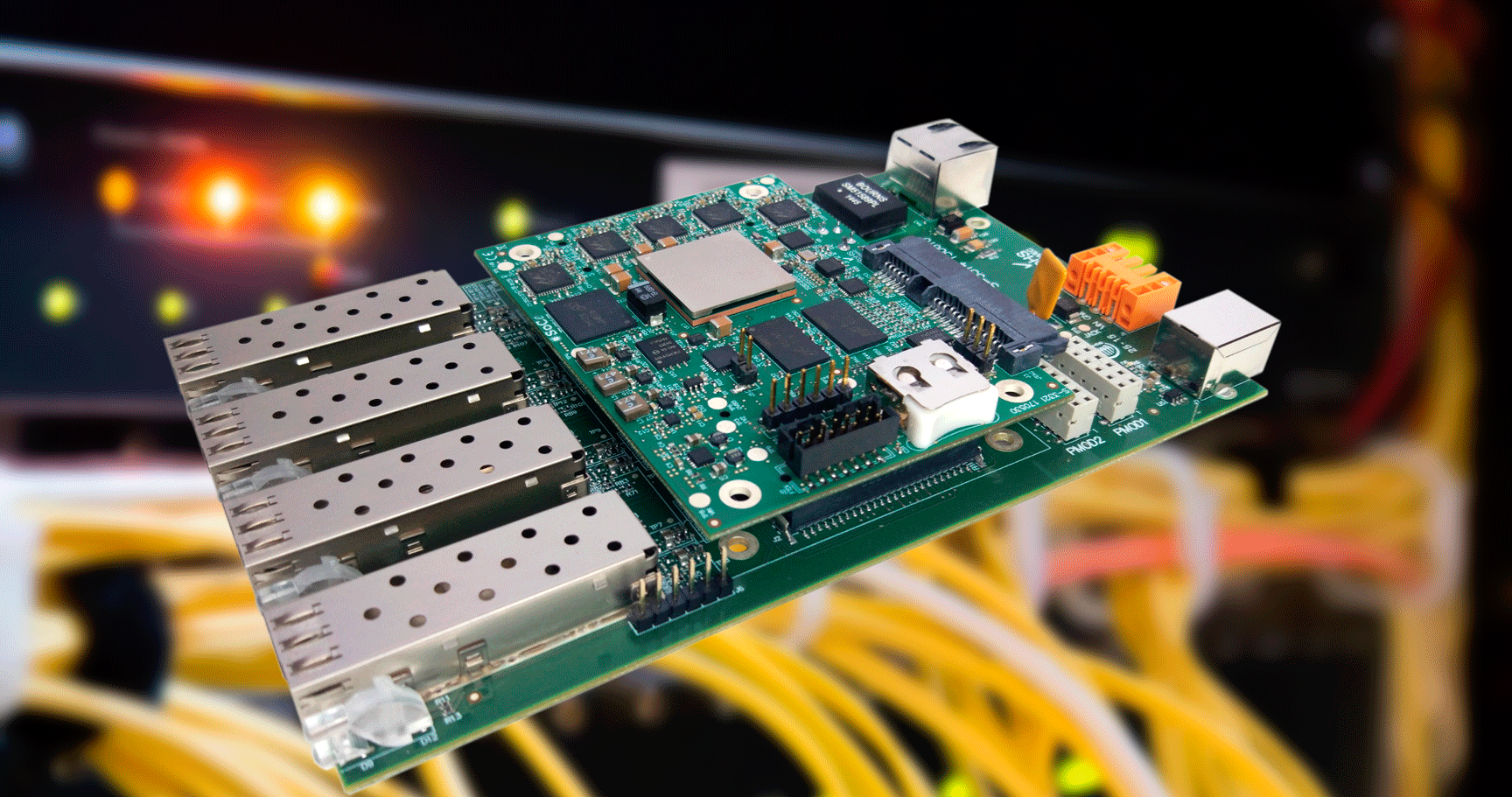

SoC-e returns with TSN to Embedded World 2024!

Window violation and jitter calculations using Time Aware Shaper in a TSN network.

SoC-e joins the PAPOS Project

Merry Christmas and a Happy New Year!

EDHPC 2023 has been a success!

We’re back from the TSN/A Conference!

Succesful time at the 15th Annual GVSETS

See you at GVSETS

SoC-e at the IEEE 802 PLENARY SESSION 2023

SoC-e Eguna 2024